- 全部

- 默认排序

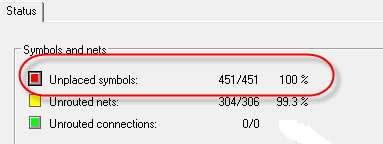

很多刚开始接触这个Allegro软件的同学,就有这样的疑问,我的原理图的网表都已经导入到PCB中了,为什么PCB板上什么都没有呢?元器件、飞线等都没有。其实,只要是网表导入到PCB中,器件都是在后台显示,需要指定元器件封装库,然后手动放置出来,下面我们详细介绍一下操作的办法:第一步,需要检查原理图的网表是否导入成功,执行菜单命令Display,在下拉菜单中选择Status,整个PCB文件的状态,如图324-1所示,进入到状态的界面,最上面一栏是Symbols and nets的选项,网表导入成功

1)单片机C忌讳绝对定位。常看见初学者要求使用_at_,这是一种谬误,把C当作ASM看待了。在C中变量的定位是编译器的事情,初学者只要定义变量和变量的作用域,编译器就把一个固定地址给这个变量。怎么取得这个变量的地址?要用指针。比如unsignedchardatax;后,x的地址就是&x,你只要查看这个参数,就可以在程序中知道具体的地址了。所以俺一看见要使用绝对定位的人,第一印象就是:这大概是个初学者。2)设置SP的问题。原因和1差不对,编译器在把所有变量和缓冲区赋予地址后,自动把最后一个字节开始

FPGA(现场可编程门阵列)自诞生以来就一直在冲击着专用集成电路(ASIC,Application Specific Integrated Circuit)芯片界的神经。在20世纪80年代中期,RossFreeman和他的同事从Zilog手中购买了这项技术,并着手创办了针对ASIC仿真和教育市场的Xilinx。(Zilog出自埃克森美孚石油公司,因为在20世纪70年代,人们已经开始担心石油会在30年后枯竭,这一点在今天仍然适用)。同时,Altera也以类似的技术为核心成立。 FPGA是由电路编程

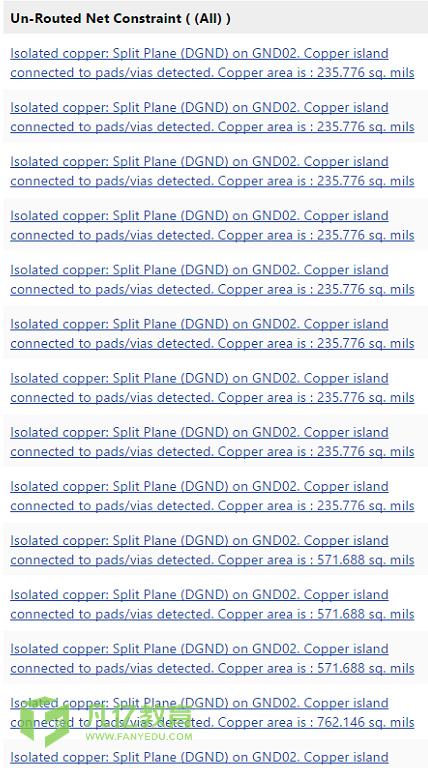

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。

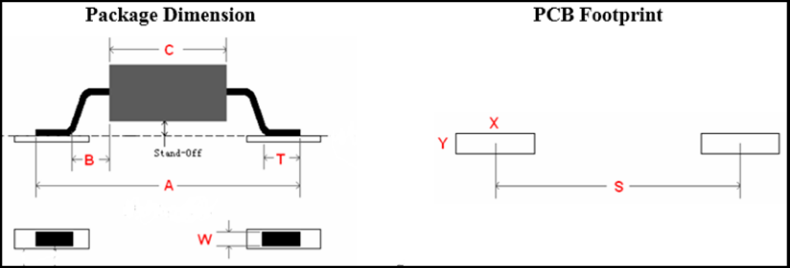

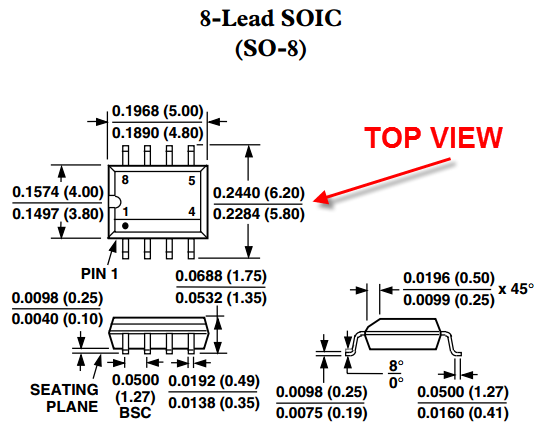

根据器件规格书(Datasheet)制作封装时,一般做出来的封装焊盘管脚长度需要做适当的补偿,即适量地对器件原先的管脚加长一点,具体的补偿方法,是根据器件的管脚类型来补偿的

我们在进行AD原理图绘制之后,都会对原理图进行编译检查。那么,当我们编译检查出现了“off grid AT.....”的警告时,总是会摸不清头脑,为什么出现了这个警告?我应该怎么去消除这个警告?

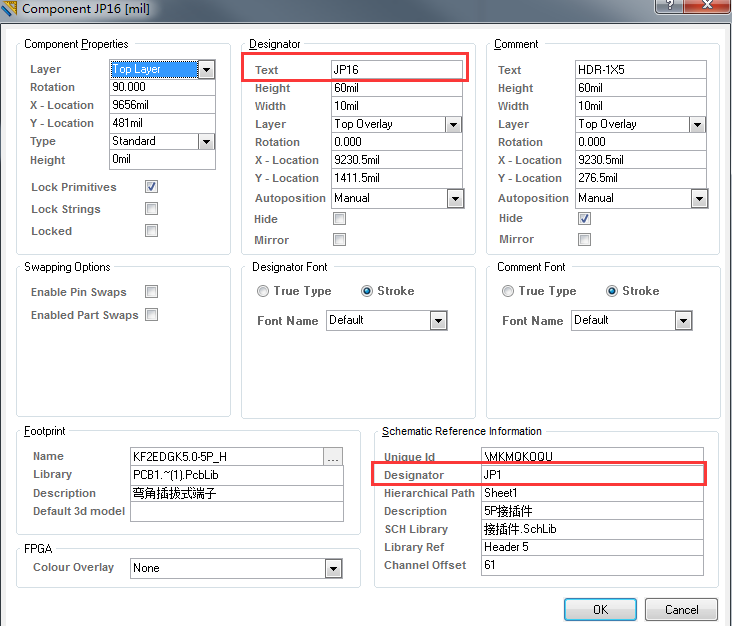

在pcb里面看上去没有Re-annotate的原因基本上是:PCB的Designator 现实的text与 Schematic的Designator出现的text名字不一致而导致的

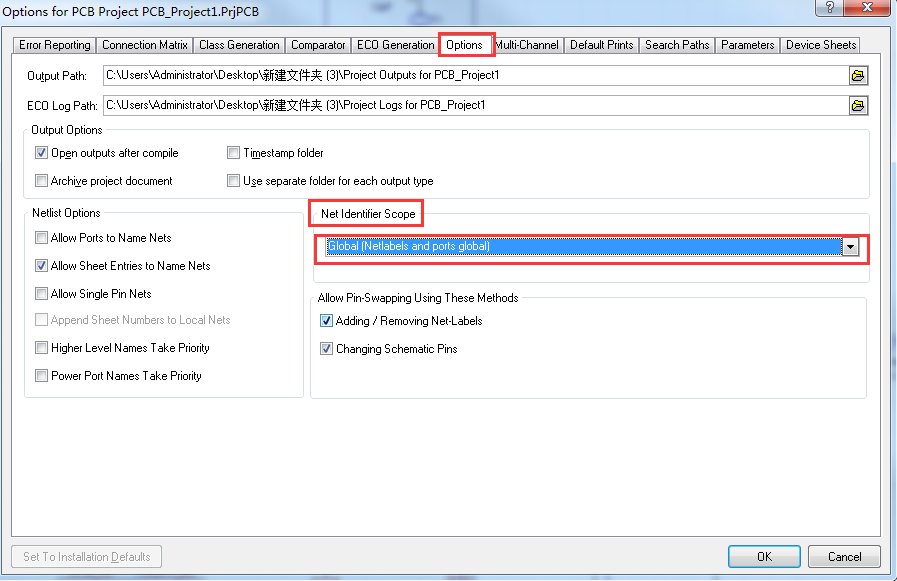

我们在日常画板子的时候,有时会出现一个比较尴尬的问题:同一个工程下不同原理图之间的相同网络标号导入到PCB文件之后,pin没有连接在一起;编译是还会出现报错,error:Duplicate Net Names。可以直接忽略,但存在报错实在让人难受。

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注